## A Basic IGBT Model with Easy Parameter Extraction

Peter O. Lauritzen

University of Washington, Seattle, WA, USA (Aalborg University, Denmark in 1999)

Gert K. Andersen

Aalborg University, Denmark

Martin Helsper

Christian-Albrechts-University of Kiel, Germany

**Abstract-** Simple parameter extraction is the goal of a new Basic IGBT model designed for use by application engineers. The model has good accuracy yet its parameters can be quickly extracted from three standard measurements or from data sheets.

### I. INTRODUCTION

For the IGBT, no compact model exists that has both reasonable accuracy and simple enough parameter extraction that an application engineer can easily determine parameters. The IGBT models currently available in common circuit simulators are either so complex that professional parameter extraction is required or so inaccurate that they are of little use in circuit simulation.

The commonly used Hefner [1,2] model available on the Saber and PSPICE simulators provides high accuracy, but parameter extraction is so complex that the extraction of parameters and creation of model libraries is practical only for simulator vendors or power semiconductor device manufacturers.

In addition to "Accurate" models like the Hefner model, "Basic" models [3] are needed where an application engineer can perform parameter extraction. Such models are suitable for general circuit simulations where reasonable static and dynamic performance is desired and high accuracy is not required. Also Basic models must be public domain so they can be available on a number of different simulators.

Suitable Basic models currently exist for all other commonly used power semiconductor devices: diode [4], MOSFET [3], SCR-GTO [5]. The lack of a commonly available, Basic level IGBT model is a major factor limiting the use of device models in power electronic circuit simulation. With only Accurate level models available, application engineers are limited to parameterized IGBT models from commercial model libraries. However, commercially extracted models are often unavailable for new or specialized devices. For converter design with these devices, application engineers must abandon the idea of simulation and resort to laboratory-based circuit design techniques.

Another use for Basic models is that of precisely matching the measured characteristics of a single specific device.

Commercially extracted models represent averaged characteristics without provision to adjust parameters to precisely match a specific device.

A number of existing IGBT models were evaluated as possible Basic models during an International Industrial and Doctoral Course in Compact Models for Power Semiconductor Devices sponsored by the Danfoss Professor Programme at Aalborg University [6]. All were rejected for one or more of the following reasons [7]:

1. The parameter extraction process was too complex.

2. The model lacked sufficient accuracy to be useful.

3. The model was proprietary and thus available only on a single simulator.

A recent review [8] of IGBT models does not use parameter extraction to classify models. One IGBT model was designed with simple parameter extraction for use in device simulators, but not for circuit simulators [9].

### II GOALS FOR A BASIC LEVEL IGBT MODEL

To meet the requirements of a new Basic IGBT model, simple, robust parameter extraction must become the primary criteria in the model design process. [7].

Five specific design goals for a future Basic IGBT model arose out of the course on compact model applications in which many of the students were working engineers from power electronic firms [6,7]. These goals for parameter extraction are based on the maximum time an application engineer can invest in extraction before needing to abandon the use of simulation in the design process.

*Goal 1: All parameters must be extractable from no more than three experimental setups.*

The three important measurement setups for an IGBT are:

*dc  $I_C$ - $V_{CE}$  characteristics*

*Gate-charge plot*

*Inductive load switching, or zero-voltage switching*

The only additional information allowed is the device data sheet. An application engineer must be able to complete all measurements and calculations within 4 hours maximum.

*Goal 2: All parameters are also extractable from data sheet information alone.*

Parameters will be less accurate, but extraction time can be limited to 0.5 hours maximum.

*Goal 3: Good static and dynamic performance*

The model should provide reasonably accurate dc characteristics at both high and low voltages. For inductive load switching, the tail current must be accurate over a wide range of collector Voltages.

*Goal 4: Available in the public domain*

The model must be available for implementation on different simulators.

### III. DESIGN OF A BASIC LEVEL IGBT MODEL

A new Buffer layer or Punch-Through IGBT model was developed to meet the above parameter extraction goals. The “Lumped-Charge” technique was chosen for ease of parameter extraction and computational efficiency [10].

In the Lumped-Charge approach, internal hole and electron charge magnitudes are calculated for only a few specific locations in the device. These charges are then linked to internal voltages and currents by exact physical equations. In this model the internal base charges are calculated only at the edges of the internal base regions to keep the model relatively simple. Examples of Lumped-Charge models for most power devices are available at [11].

The internal BJT is modeled with physically based equations while empirical equations suffice for the internal MOSFET. Physical features in the model include: base region charge storage and recombination, base transport equation for low and high level injection, junction emitter efficiency, base-width modulation limited by punch-through at high collector voltages, collector-gate and collector-emitter capacitance variation, emitter parasitic resistance and inductance. The gate-emitter capacitance is constant.

The model equations are given in the Appendix. The equations were implemented in the Saber MAST HDL (Hardware Description Language) and the source code is available for public downloading from the Web [11].

### IV. PARAMETER EXTRACTION

For ease of use, the parameters are generally expressed in terms of familiar electrical quantities rather than expressions from device physics. Table 1 lists the 17 model parameters, of which 11 determine the dc and transient conduction characteristics and 6 determine the capacitances and emitter parasitic inductance and resistance.

TABLE 1

PARAMETERS FOR IGBT MODEL

| Parameter | Description                                         | Units             |

|-----------|-----------------------------------------------------|-------------------|

| $k_p$     | MOSFET transconductance coefficient                 | A                 |

| $k_v$     | Turn-on Voltage fitting parameter                   | n.u.              |

| $V_T$     | Threshold Voltage for turn-on                       | V                 |

| $b$       | Fitting parameter for MOSFET transconductance       | n.u.              |

| $V_j$     | Built-in Voltage for p-n junctions                  | V                 |

| $V_{PT}$  | IGBT internal punch-through Voltage                 | V                 |

| $I_{LH}$  | Threshold between high and low level injection      | A                 |

| $T_0$     | Base transit time                                   | s                 |

| $\tau_B$  | Base carrier lifetime                               | s                 |

| $\tau_E$  | Internal emitter efficiency expressed as a lifetime | s                 |

| $R_H$     | High Voltage & current charge compensation          | Ohms              |

| $R_E$     | Emitter parasitic series resistance                 | Ohms              |

| $L_E$     | Emitter parasitic series inductance                 | H                 |

| $C_{ox}$  | Gate-Collector oxide capacitance                    | F                 |

| $\gamma$  | Gate-Collector body effect coefficient              | $V^{\frac{1}{2}}$ |

| $C_{ge0}$ | Gate-Emitter capacitance                            | F                 |

| $C_{ce0}$ | Collector-Emitter capacitance                       | F                 |

#### A. Extraction of Capacitance Parameters

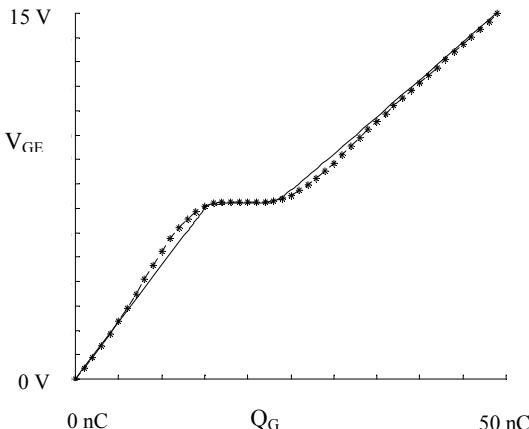

The four capacitance parameters  $C_{ge0}, C_{ox}, \gamma, C_{ce0}$  can be extracted from the gate-charge plot shown in Figure 1 where the horizontal scale represents charge  $Q_G = I_G * t$ .

The inverse slope increasing from  $V_{GE} = 0$  represents  $C_{ge0}$ , the gate-emitter capacitance. The inverse slope to the right of the flat “Miller effect” region represents  $C_{ox} + C_{ge0}$  where  $C_{ox}$  is the gate-collector oxide capacitance. The change in charge in the flat region  $\Delta Q$  is used to calculate the body-effect

$$\text{parameter gamma where } \gamma = \frac{\Delta Q}{C_{ox}} - V_{CG \min} \quad (1)$$

Here  $V_{CEsat} - V_{GE} = V_{CG \min}$  is the minimum collector-gate Voltage at the right end of the horizontal region in Fig. 1 and  $V_{CC} - V_{GE} = V_{CG \max}$  is the maximum at the left end.

The collector-emitter capacitance parameter  $C_{ce0}$  can be extracted from data sheet plots of output  $C_{OES}$  and transfer  $C_{RES}$  capacitances evaluated at zero collector Voltage.

$$C_{ce0} = C_{OES} - C_{RES} \quad (2)$$

Figure 1: Gate-charge plot.

Intersil 12N60B3D data sheet: dotted line.

Simulation: solid line.

### B. Extraction of Conduction Parameters

The conduction parameters are inter-related in their effect on performance, so some optimization is required to extract all of them. Some basic assumptions on IGBT operation can be made to enable a relatively simple, but approximate parameter extraction.

Two extraction procedures are proposed: one using a relatively simple procedure, and the other a more accurate procedure using a simple MATLAB routine for optimization. The optimization routine provides somewhat better results at low currents and Voltages. Only the simple extraction procedure is described in this paper; the MATLAB code for optimization can be obtained from [11].

The first step is to obtain data from a reverse recovery measurement with clamped inductive load using a low Voltage collector supply (10 or 20 V.).

The time constant that is observed for the exponentially decreasing tail current is the effective lifetime  $\tau_{eff}$ , where

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_E} + \frac{1}{\tau_B}. \quad (3)$$

Knowing  $\tau_{eff}$ , and  $I_{C1}$ , the current value at the beginning of the tail current and  $I_C$ , the initial collector current, the low voltage base transit time  $T_0$  can be calculated as

$$T_0 = \tau_{eff} \left( \frac{I_C}{I_{C1}} - 1 \right). \quad (4)$$

Since most punch-through IGBTs operate with their gain limited by emitter efficiency, the base lifetime  $\tau_B$  can be given the value of  $\tau_B \approx 10\tau_E$  where  $\tau_E$  is the internal emitter

efficiency expressed as a lifetime. These parameters must be given non-zero values for numerical convergence. Then from a plot of the dc  $I$ - $V$  characteristics at low Voltages one can determine both the coefficient  $k_p$  and the fitting parameter  $b$ . Above the pinch-off voltage

$$\frac{I_C}{2} = \frac{k_p}{2} \left( \frac{V_{GE}}{V_T} - 1 \right)^b \quad (5)$$

The pinch-off Voltage  $V_T$  can be extracted from a plot of  $I_c^{1/b}$  versus  $V_{GE} = V_{CE}$ , where  $b$  is adjusted to obtain a straight line. The value of the built-in Voltage parameter  $V_J$  should be adjusted to provide a best match to the IGBT collector-emitter turn-on Voltage.

Since IGBTs are normally operated at high level injection,  $I_{LH}$ , the boundary current between high level and low level injection operation should be set to a value two or three times lower than the normal collector currents being used. Or, the collector Voltage rise time  $t_{d(OFF)}$  during high voltage inductive load turn-off can be used to determine  $I_{LH}$ .

$$I_{LH} = -\frac{I_C t_{d(OFF)}}{2\tau_E \ln \left( 1 - \sqrt{\frac{V_{CC}}{V_{PT}}} \right)} \quad (6)$$

where,  $V_{CC}$  is the collector supply Voltage. Set the punch-through Voltage  $V_{PT} \equiv B_{VCEs}$ , the breakdown Voltage. Set the parameters  $k_V = 1$ ,  $r_H = 0$  and make  $R_E$  small unless optimization is used.

The emitter parasitic inductance  $L_E$  can be estimated from the slope of the turn-off current prior to the start of tail current.

$$L_E = (1.3V_T - V_{GEoff}) \left/ \frac{dI_C}{dt} \right. \quad (7)$$

Another method for extraction of  $L_E$  is described in [12].

Given the necessary experimental set-ups, the total time for all measurements is one to two hours. Extraction of the parameters from the measured data requires another hour. Some additional time needs to be allotted for simulation testing of the model. So, the total time needed for extraction and measurements is three to four hours, depending upon the experience of the person doing the extraction.

### C. Extraction from Only a Data Sheet

Extraction from data sheet information alone is less accurate because only high Voltage transient measurement data is available. The physics of a turn-off transient at high Voltage is more complex because the IGBT base width changes rapidly during turn off. Using (6) the collector Voltage rise time  $t_{d(OFF)}$  can be used to determine  $\tau_E$ , assuming

$I_{LH} \approx \frac{I_C}{4}$  and  $T_0 = 3\tau_E$ . These approximations are necessary because other suitable data is unavailable. Only approximate results are expected from this process.

The dc data on the data sheet can be used to determine  $k_P$ ,  $V_T$  and  $b$  using the procedure in the previous section.

#### V. COMPARISON WITH MEASUREMENTS

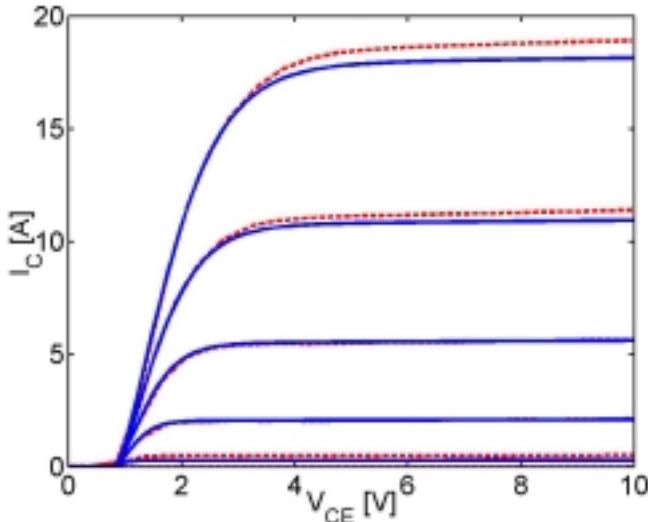

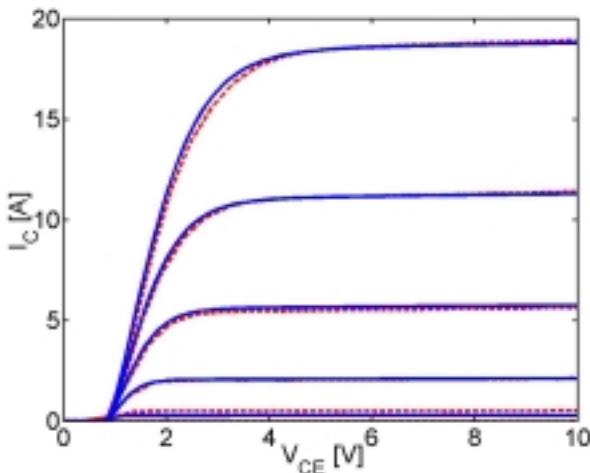

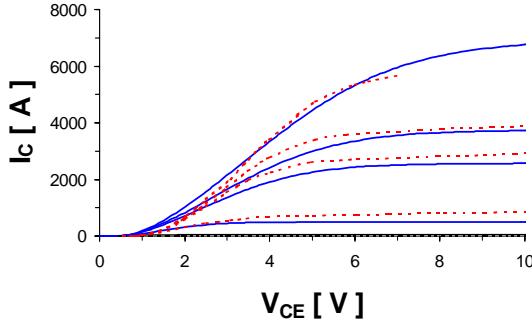

Comparisons were made with dc  $I_C$  -  $V_{CE}$  plots and inductive load switching measurements on an Intersil 12N60B3D. Figures 2 and 3 compare the dc characteristics obtained using the simple MATLAB optimization with characteristics obtained through further adjustments of  $I_{HL}$ , and  $R_E$ .

Figure 2. dc  $I_C$ - $V_{CE}$  plot using simple optimization.

Measurements: dashed; simulated: solid lines

Figure 3. dc  $I_C$ - $V_{CE}$  plot using adjusted parameters.

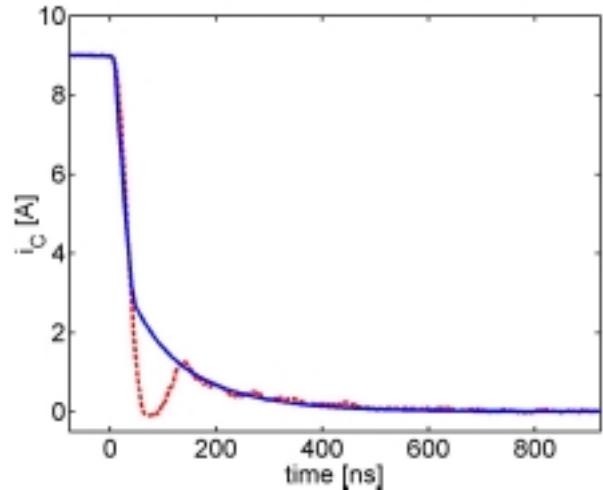

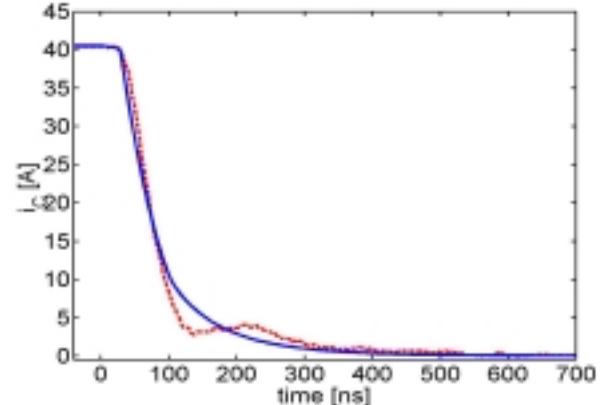

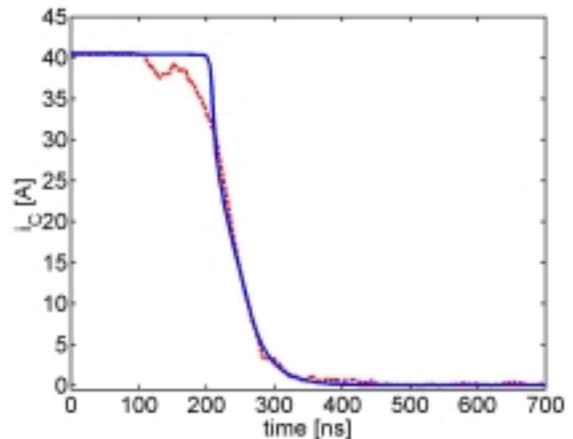

Figure 4. Collector current inductive load turn-off at  $I_C = 9$  A. and  $V_{CE} = 18$  V adjusting for  $L_E$  parameter.

Measurements: dashed; simulated: solid lines. The dip in the measured data is due to diode forward recovery.

Figure 5. Collector current inductive load turn-off at  $I_C = 40$  A. and  $V_{CE} = 100$  V. adjusting for  $L_E$  parameter.

Figure 6. Collector current inductive load turn-off at  $I_C = 40$  A. and  $V_{CE} = 400$  V. adjusting for  $L_E$  parameter.

Figures 4,5, and 6 show current waveforms for inductive load turn-off obtained by the same optimization process plus further adjusting of  $I_{HL}$ ,  $L_E$  and  $R_E$ . Note the excellent match between measured and simulated waveforms over a wide range of collector voltages.

To evaluate model performance on a high Voltage, high current IGBT, measurements were made on a Mitsubishi CM1200HA-34H IGBT. Parameters were adjusted informally without optimization. Figures 7 shows the dc characteristics.

Figure 7. dc  $I_C$ - $V_{CE}$  plot using simple parameter extraction.

Measurements: dashed; simulated: solid lines

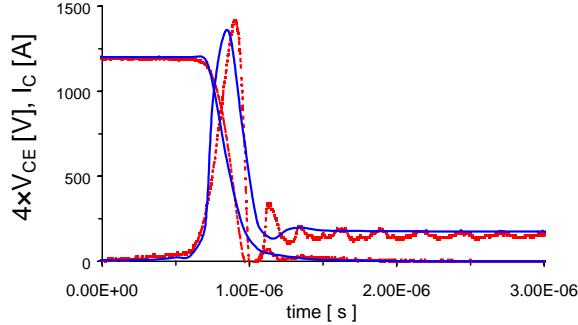

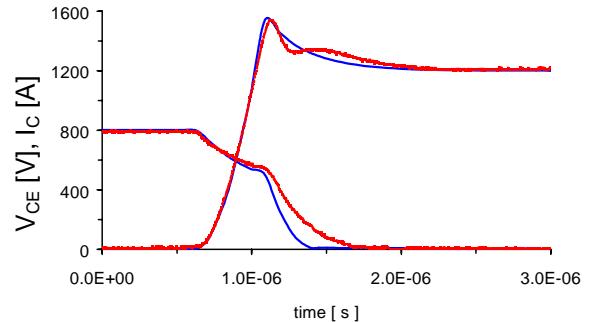

Figure 8. Collector current inductive load turn-off at  $I_C=1200$  A. and  $V_{CE}=42$  V adjusting for  $L_E$  parameter.

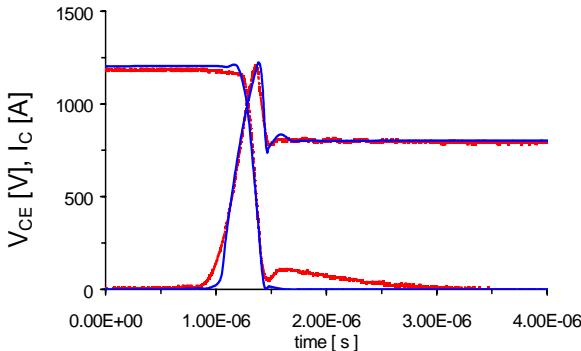

Measurements: dashed; simulated: solid lines.

Figure 9. Collector current inductive load turn-off at  $I_C=1200$  A. and  $V_{CE}=800$  V.

Measurements: dashed; simulated: solid lines.

Figure 10. Collector current inductive load turn-on at  $I_C=1200$  A. and  $V_{CE}=800$  V.

Figures 8 and 9 show inductive load turn-off waveforms at 42 V. and 800 V. and Figure 10 shows turn-on characteristics at 800 V. The switching characteristics match very well except for some of the tail current data.

## VI CONCLUSIONS

For a complex physical device like an IGBT, a suitable Basic model with simple parameter extraction is possible. Now, Basic models are available for all commonly used power semiconductor devices.

A parameter optimizer that uses a larger set of parameters should produce better results in the extraction procedure

With some changes in the parameter extraction, this model also should be valid for non-punch-through IGBTs, but this has not been validated.

## VII APPENDIX: LIST OF MODEL EQUATIONS

In the equations, true voltages are expressed as " $v$ ", while " $u$ " quantities are voltages normalized to the thermal voltage  $\phi_t$ .

### A. Emitter Parasitic Resistance and Inductance Equations

$$\text{Gate-internal emitter voltage } v_{GEi} = v_{GE} - v_{Ei} . \quad (\text{A1})$$

$$\text{Internal emitter voltage } v_{Ei} = i_E r_E + L_E \frac{di_E}{dt} . \quad (\text{A2})$$

### B. Capacitance and Voltage Equations

$$\text{Collector-emitter voltage } u_{CE} = u_{34} + u_{45} + u_{5Ei} + \frac{v_{Ei}}{\phi_t} . \quad (\text{A3})$$

Emitter-base depletion charge

$$q_{56} = 2C_{ce0}V_J \sqrt{1 + \frac{u_{5Ei}}{U_J}} \quad \text{for } u_{5Ei} \geq 0$$

$$q_{56} = C_{ce0} \left[ 2V_J + \phi_t u_{5Ei} \left( 1 - \frac{u_{5Ei}}{4U_J} \right) \right] \text{ for } u_{5Ei} \leq 0 \quad (\text{A4})$$

$$\text{Emitter-base capacitive current } i_{Cce} = \frac{dq_{56}}{dt} \quad (\text{A5})$$

$$\text{Collector-base depletion charge } q_{34} = 2\phi_t C_{ce0} u_{34} \quad (\text{A6})$$

$$\text{Collector-base capacitive current } i_{Cab} = \frac{dq_{34}}{dt} \quad (\text{A7})$$

$$\text{Base-gate voltage } u_{5G} = u_{5Ei} - u_{GEi} \quad (\text{A8})$$

$$\text{Depletion & oxide voltages } u_{5G} = u_{dep} + u_{ox} \quad (\text{A9})$$

$$\text{Gate bulk charge } q_{CG} = \pm q_{CG0} \sqrt{e^{-u_{dep}} + u_{dep} - 1} \quad (\text{A10})$$

$$\text{Base-gate oxide voltage } u_{ox} = \frac{q_{CG}}{C_{ox} \phi_t} \quad (\text{A11})$$

$$\text{Gate-collector capacitive current } i_{Ccg} = + \frac{dq_{CG}}{dt} \quad (\text{A12})$$

$$\text{Gate-emitter capacitive current } i_{Cge} = C_{ge0} \frac{dv_{GEi}}{dt} \quad (\text{A13})$$

### C. Current Equations

$$\text{MOSFET current } i_D = 0 \text{ for } v_{GEi} \leq V_T \quad (\text{A14})$$

$$i_D = \frac{k_p}{2} \left( \frac{v_{GEi}}{V_T} - 1 \right)^b \tanh \left( \frac{k_v \phi_t u_{5Ei}}{v_{GEi} - V_T} \right) \text{ for } v_{GEi} > V_T$$

$$\text{Collector current } i_A = i_{p34} + i_{n34} + i_{Cab} \quad (\text{A15})$$

$$\text{Collector current } i_A = i_{p46} + i_{n45} \quad (\text{A16})$$

$$\text{Base electron current } i_{n45} = i_{ce} + i_D + i_{Ccg} + i_{n56} \quad (\text{A17})$$

$$\text{Base charge } i_{p34} - i_{p46} = \frac{(q_{p4} - Q_{pB})y}{\tau_B} + \frac{dq_{p4}y}{dt} \quad (\text{A18})$$

$$\text{Collector electron current } i_{n34} = I_{CS} [\exp(u_{34}) - 1] \quad (\text{A19})$$

$$\text{Emitter electron current } i_{n56} = -I_{CS} [\exp(-u_{5Ei}) - 1] \quad (\text{A20})$$

### D. Variable Base Width Calculations

$$\text{Smoothing function } u_{\text{lim}} = \exp \left[ 40 \left( \frac{u_{5Ei}}{u_{PT}} - 0.87 \right) \right] \quad (\text{A21})$$

$$yu = \frac{\left[ \frac{(\frac{V_J}{\phi_t} + u_{5Ei})}{u_{PT} + (i_{p46} - i_D) \frac{r_H}{\phi_t}} \right] + 0.9u_{\text{lim}}}{1 + u_{\text{lim}}} \quad (\text{A22})$$

$$\text{Base transit time variation } T = T_0 (1 - \sqrt{yu}) \quad (\text{A23})$$

### E. Diffusion Charge Calculations

$$\text{Base charge at emitter } q_{p5} = Q_{pB} \exp(-u_{5Ei}) \quad (\text{A24})$$

$$\text{Charge at collector } q_{p4} (q_{p4} + Q_B) = Q_i^2 \exp(u_{34}) \quad (\text{A25})$$

$$\text{Base hole current } i_{p46} = \frac{q_{p4} - q_{p5}}{T} + \frac{q_{p4}}{T} u_{45} \quad (\text{A26})$$

$$\text{Electron current } i_{n45} = \frac{q_{p5} - q_{p4}}{T} + \frac{(q_{p4} + Q_B)}{T} u_{45} \quad (\text{A27})$$

### F. Terminal Currents

$$\text{Gate current } i_G = -i_{Ccg} + i_{Cge} \quad (\text{A28})$$

$$\text{Current } \text{out} \text{ of the emitter } i_E = + (i_G + i_C) \quad (\text{A29})$$

Internally calculated parameters:

$$Q_B = 2T_0 I_{LH}, Q_i = \frac{Q_B}{\sqrt{\exp(U_J)}}, I_{CS} = \frac{Q_i^2}{Q_B \tau_E},$$

$$Q_{pB} = \frac{Q_i^2}{Q_B}, q_{AG0} = C_{ox} \gamma \sqrt{\phi_t}.$$

## VII REFERENCES

- [1] A.R. Hefner and D.M. Diebolt, "An experimentally verified IGBT model implemented in the Saber simulator", *IEEE Trans. Pwr.Elec.*, Vol.9, No. 5, pp.532-542, Sept. 1994.

- [2] A.R. Hefner, "Modeling buffer layer IGBTs for circuit simulation", *IEEE Trans. Pwr.Elec.*, Vol. 10, pp.111-123, March. 1995.

- [3] I. Budihardjo, P. O. Lauritzen, K. Y. Wong, R. B. Darling, H. Alan Mantooth, "Defining Standard Performance Levels for Power Semiconductor Devices", *IEEE IAS Annual Meeting*, October 1995.

- [4] P.O. Lauritzen and C.L. Ma, "A simple diode model with reverse recovery", *IEEE Trans. Pwr. Elec.*, vol. 6, pp.188-191, April 1991.

- [5] K.L. Wong, P.O.Lauritzen et al., "An SCR-GTO model designed for a basic level of performance", *Proc. IEEE IAS Annual Meeting*, San Diego, CA, October 1996.

- [6] Danfoss Professor Programme, Aalborg University, Denmark, <http://www.iet.auc.dk/danprof/>

- [7] P.O. Lauritzen, G. K. Andersen, P.D. Chandana Perera, Subramanian R., K.N. Bhat, "Goals for a Basic level IGBT model with easy parameter extraction", *Proc. IEEE Workshop Computers in Pwr. Elec.*, July 2000, pp. 91-96.

- [8] K. Sheng, B.W. Williams, "A review of IGBT models", *IEEE Trans. Pwr. Elec.*, vol. 15, pp.1250-1266, Nov. 2000.

- [9] S. Azzopardi, M. Trivedi, C. Zardini, K. Shenai, "A punch-through IGBT model using a simple technological parameters extraction method for two-dimensional physical simulation", *Euro. Pwr.Elec.Conf.*, 1999

- [10] C. L. Ma, P. O. Lauritzen, J. Sigg, "Modeling of Power Diodes with the Lumped-Charge Modeling Technique", *IEEE Trans. Pwr. Elec.*, Vol. 12, No. 3, pp. 398-405, May 1997.

- [11] <http://www.ee.washington.edu/research/pemodels/>

- [12] M. Trivedi, K. Shenai, "Parasitic extraction methodology for IGBTs", *IEEE APEC Proc.* Feb. 2000.